使用51单片机的前言之友会知道:编写程序时,需要关闭51单片机的电源,然后再打开。使用过STM32单片机的朋友会知道:编写程序时需要设置启动模式。

ESP8266还需要在编程时手动设置模式。 STM32具有ISP自动下载电路,ESP8266是否具有自动下载电路?答案是肯定的。

让我们在下面进行分析。自动下载电路设计ESP8266进行下载时,发现每次都需要设置GPIO0的状态。

如何实现GPIO0电平状态的自动切换?查看下面的电路。可以看出,该下载电路是相对于普通的CH340G下载电路而言的。

该电路将CH340G芯片的DTR和RTS引脚引到两个S8050晶体管,以控制nRST和GPIO0的电平。 ESP8266下载模式根据ESP8266芯片数据所需的下载过程,仅当GPIO0为低电平时复位芯片时,才能进入USART下载模式。

让我们看一下自动下载电路如何实现此过程的顺序。首先,我们仍然必须从分析核心设备CH340G开始。

核心设备CH340系列CH340G是USB到串行集成芯片。关键性能参数如下:您可以在数据手册中看到引脚说明:DTR#引脚是MODEM触点输出信号,数据端子已准备好,并且低(高)有效。

作为USB配置完成之前的配置输入引脚,可以连接4.7KΩ的下拉电阻,以在USB枚举期间生成默认的低电平。 RTS#引脚MODEM触点输出信号,请求发送,低(高)有效。

这两个MODEM接触信号由计算机应用程序控制,并且定义了它们的用途。发行软件并单击下载按钮后,通常将DTR#拉低,将RTS拉高,经过一段时间后,将DTR#拉高。

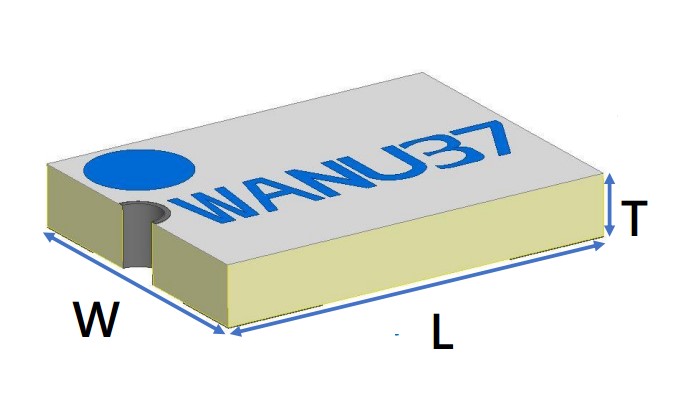

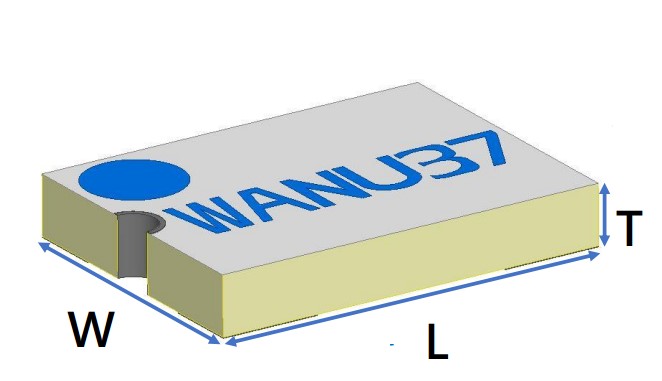

,RTS#返回低电平。注意:新设计的电路板可以选择CH340C,它具有内置的晶体振荡器,不需要外部晶体振荡器。

从示意图中,我们可以看到两个引脚的逻辑电路连接如下:端口真值表根据该电路,我们可以知道,当DTR为1时,RTS为0时,nRST复位引脚被拉低,否则,GPIO0引脚下拉,结果逻辑关系图如下:这样,单击下载按钮后,CH340G芯片的DTR为低电平,RTS为高电平。此时,ESP8266的GPIO0被拉低,复位RST信号为高电平。

ESP8266进入下载模式。反转CH340G的DTR和RTS电平后,RST为0,GPIO0变为1,ESP8266进入Flash操作模式,程序正常运行。

这样就实现了ESP8266的自动下载。免责声明:本文内容经21ic授权后发布,版权归原作者所有。

该平台仅提供信息存储服务。本文仅代表作者的个人观点,并不代表该平台的立场。

如有任何疑问,请与我们联系,谢谢!。

公司: 深圳市捷比信实业有限公司

电话: 0755-29796190

邮箱: momo@jepsun.com

产品经理: 聂经理

QQ: 2215069954

地址: 深圳市宝安区翻身路富源大厦1栋7楼

更多资讯

获取最新公司新闻和行业资料。

- double sum = 0.0; for(int i = 0; i < n; i++) { if(resistors[i] > 0) { sum += 1.0 / resistors[i]; 在C语言中计算并联电阻的总电阻是一个常见的应用问题,它涉及到基本的物理知识与编程技巧的结合。并联电路中的总电阻可以通过所有并联电阻倒数的和的倒数来计算。首先,我们需要定义一个函数来处理这一计算过程。例如...

- GYD5-6.3/A:一种高效可靠的气压自动开关 GYD系列气压自动开关是一种高效、可靠的电气控制设备,其中GYD5-6.3/A型号具有广泛的应用场景。这种自动开关主要应用于工业生产过程中,对气体压力进行监测和控制,确保系统的稳定运行。GYD5-6.3/A采用先进的设计理念和技术制...

- 德国P+F接近开关:工业自动化中的关键组件 德国P+F接近开关是工业自动化领域中不可或缺的一部分,它们被广泛应用于各种机械设备和生产线上,以实现非接触式的物体检测。这种传感器通过电磁场或射频技术来识别目标物体,无需与物体直接接触即可检测其存在与否,...

- 德国福P+F接近开关:自动化控制领域的高效解决方案 德国福P+F公司是世界著名的传感器制造商之一,其生产的接近开关在自动化控制领域拥有极高的声誉。福P+F接近开关采用先进的传感技术,能够在无需物理接触的情况下检测到目标物体的存在,这不仅减少了机械磨损,还大大提...

- 德国P+F电感式接近开关:工业自动化的关键组件 德国P+F(*福)是一家在传感器技术和自动化领域享有盛誉的公司。其电感式接近开关作为产品线中的重要一员,在工业自动化控制领域扮演着关键角色。这种类型的接近开关利用电磁感应原理来检测金属物体的存在与否,无需与目...

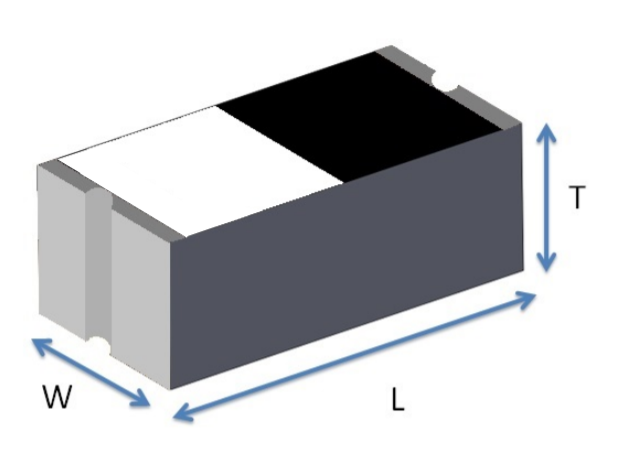

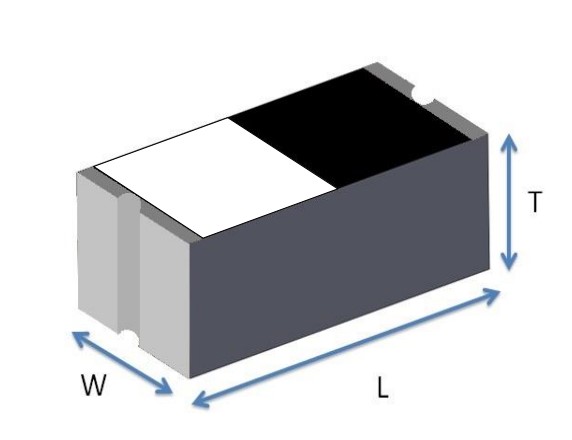

- 深入解析6/16V BF系列SMD电阻在高密度PCB设计中的应用价值 6/16V BF系列SMD电阻:高密度板设计的理想之选随着电子产品向小型化、轻量化方向发展,印刷电路板(PCB)的设计密度不断提升。在此背景下,6/16V BF系列SMD电阻凭借其卓越的尺寸适应性和电气性能,成为高密度集成电路设计中的...

- Elprocus 的 4、5、6 波段电阻颜色代码计算器 众所周知,电阻器是一个基本元件,我们可以在任何电子电路中找到它。电阻器的电阻值取决于它所使用的应用类型。尽管当今市场上有先进的电阻测量设备,但电阻器的颜色代码系统总是使我们能够轻松读取和识别其电阻值。...

- 从16V BMF到6/16V BF系列:SMD电阻在高密度PCB设计中的关键作用 前言:高密度电路板对元器件的新挑战随着电子产品向轻薄短小发展,印刷电路板(PCB)的布线密度不断提高,这对元器件提出了更高要求——不仅要体积小、性能稳,还需具备良好的热管理能力和长期可靠性。在此背景下,16V...

- 如何在8V~29V系统中正确设计P/N沟道MOS管驱动电路 引言:驱动电路的重要性在8V至29V的电力电子系统中,正确设计MOS管的栅极驱动电路是确保器件稳定、高效运行的关键环节。无论是P沟道还是N沟道器件,若驱动不当,可能导致导通不完全、开关速度慢甚至击穿损坏。核心设计原...

- Wi-Fi 6天线2.4G+5G双频天线技术详解与应用 在当今数字化时代,Wi-Fi技术的发展日新月异,Wi-Fi 6作为最新的无线网络标准,不仅显著提升了数据传输速度和连接稳定性,还通过引入2.4G和5G双频段天线技术,进一步优化了网络性能。2.4G和5G双频天线技术是Wi-Fi 6的关键组成部...

- Wi-Fi 6双频天线技术解析:2.4G与5G频段协同提升网络性能 Wi-Fi 6双频天线技术的核心优势随着无线网络需求的持续增长,Wi-Fi 6(802.11ax)标准应运而生,其核心之一便是支持2.4GHz和5GHz双频段协同工作。搭载2.4G+5G双频天线的设备能够智能切换频段,有效缓解网络拥堵,显著提升传输速率...

- Wi-Fi 6天线详解:2.4G与5G双频天线如何提升网络性能? Wi-Fi 6天线技术解析:2.4G与5G双频天线的协同优势随着智能设备的普及和对高速网络需求的不断增长,Wi-Fi 6(IEEE 802.11ax)成为新一代无线网络标准的代表。其中,支持2.4G与5G双频的天线设计,是实现高性能、低延迟网络体验的关...

- 单信道栅极驱动器在P沟道MOS管驱动设计中的应用与优化 单信道栅极驱动器在P沟道MOS管驱动设计中的核心作用在现代电力电子系统中,尤其是电源管理、电机控制和开关电源(SMPS)等应用中,P沟道MOS管因其高侧开关特性被广泛使用。然而,其栅极驱动要求较为特殊,需精确控制栅源...

- 6/16V BF系列发动机技术参数与应用分析 在现代发动机技术中,6/16V BF系列因其独特的设计和卓越的性能而受到广泛关注。这一系列发动机主要用于大型船舶和工业设备中,其特点在于采用了双排16缸V型布局,能够提供强大的动力输出,同时通过优化燃烧效率来减少燃油...

- 费斯托Festo PEV-W-KL-压力开关:工业自动化领域的高效解决方案 费斯托Festo的压力开关PEV-W-KL-是一款高性能的设备,被广泛应用于工业自动化领域。这款压力开关设计紧凑,具有高度的可靠性和精确度,能够在各种恶劣环境下稳定工作。PEV-W-KL-型号的压力开关适用于监测气体或液体的压力,并...

- Wi-Fi 6双频天线优势详解:为何它成为新一代网络设备标配? Wi-Fi 6双频天线:构建高效、稳定无线网络的核心组件在当前万物互联的时代,网络连接的稳定性与速度成为用户体验的关键。Wi-Fi 6双频天线凭借其在2.4GHz与5GHz双频段上的卓越表现,正迅速成为智能手机、路由器、智能电视等主...

- P沟道MOS管栅极驱动设计中的常见问题与解决方案 P沟道MOS管栅极驱动设计中的典型问题分析尽管P沟道MOS管在高侧开关中具有优势,但在实际应用中常因驱动不当导致性能下降甚至器件损坏。以下是常见的驱动设计问题及其应对策略。1. 栅极电压不足导致导通不充分当栅极电压未...

- 气压自动开关GYD20—2:高效稳定的自动化控制解决方案 气压自动开关GYD20—2是一种高效、可靠的自动化控制设备,广泛应用于各种需要根据气压变化进行自动控制的场合。该产品具备灵敏度高、响应速度快、稳定性好等特点,能够准确地感应到系统内的气压变化,并及时做出相...

- 深入理解P沟道MOS管:从原理到典型电路设计应用 什么是P沟道MOS管?P沟道MOS管(PMOS)是一种以空穴为主要载流子的场效应晶体管,属于增强型或耗尽型器件,常见于集成电路和电源管理模块中。其核心特征是:在栅极施加相对于源极的负电压时,沟道形成并导通电流。1. PMOS的...

- P沟道MOS管工作原理与应用解析:从基础到实际电路设计 P沟道MOS管概述P沟道金属氧化物半导体场效应晶体管(P-channel MOSFET)是一种以空穴为多数载流子的场效应器件,广泛应用于电源管理、开关控制和模拟电路中。其核心优势在于低导通电阻和高开关速度,尤其在需要负电压驱动的...