& nbsp;数字电视地面广播编码正交频分复用COFDM传输系统因其强大的抗多径干扰性能和易于实现的移动接收而在HDTV研究中占有非常重要的地位。 COFDM系统中的编码和解码技术是影响系统性能的重要因素。

本文基于最大似然解码-维特比VB解码算法的思想,并从FPGA实现的角度讨论了COFDM系统中内部码(收缩卷积码)的解码。 1设计算法的简要说明在HDTV地面广播COFDM系统中,使用的内部代码是删余的卷积代码。

除了1/2的主要编码率外,还有2 / 3、3 / 4、5 / 6和7/8的编码率。卷积编码。

在实际的传输通道中,噪声通常是加性高斯白噪声(AWGN),并且AWGN通道的输入是二进制信号序列。为了充分利用信道输出信号的信息并提高传输系统的解码的可靠性,首先对信道的输出信号进行量化,并且将Q电平量化序列输入到维特比解码器。

因此,本文中使用的VB解码算法是一种软判决代码算法。 1.1主码率为1/2的卷积码编码目前,在国际卫星通信和许多通信系统中,(2,1,6)码是使用VB解码的首选标准卷积码。

由于此代码可以最大程度地降低误码率并克服相位误差,因此在HDTV地面广播COFDM传输系统中,内部代码采用(2,1,6)码,其子生成器为(171,133),全部八进制。相应的生成多项式G D = 1 + D + D2 + D3 + D6 1 + D2 + D3 + D5 + D6 df = 10。

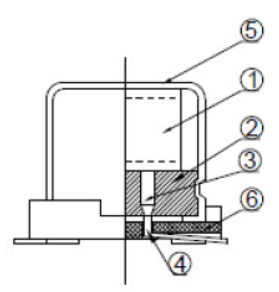

编码器的框图如图1所示。由于(2,1,6)代码具有64种状态,为了直观起见,使用列表方法来表示其围栏图,如表1所示。

; nbsp; 1.2穿孔卷积码的实现为了实现多速率传输,当提高码率时,解码器的复杂度将不会增加。在此设计中,添加和删除了(2,1,6)代码。

于(删节)。如图1所示,在进行上述编码之后,将删除输出码字中的特定位置。

以此方式,可以生成具有更高的码率2 / 3、3 / 4、5 / 6和7/8的卷积码。 1.3 Viterbi解码算法的简要介绍Viterbi VB解码算法是最大似然解码算法。

在接收端的解码过程中,根据接收到的符号的处理方法不同,分为硬判决解码和软判决解码。在相同的解码算法下,尽管硬判决解码比软判决解码更容易实现,但性能会损失2到3 dB。

因此,本文基于软决策讨论了FPGA的实现。具体算法如下:(1)从某个时间单位j = m开始,计算进入每种状态的分支长度为j的所有局部路径的局部路径度量。

对于64个州中的每个州,请选择并存储具有最大度量标准的部分路径并将部分度量标准值存储为剩余的所选路径。 (2)将j加1,将此时进入每个状态的所有分支度量添加到上一次连接到这些分支的其余选择路径的度量中,以获得此时进入每个状态的保留路径,并存储它们,然后删除所有其他路径。

(3)为了在FPGA设计中达到更高的时钟速度,在判断和输出路径寄存器的信息时,本文取出所有64个路径寄存器的第一条信息元素,并根据输出第一条信息。对大量决策标准元。

2 Viterbi解码的FPGA实现本文是在Altera公司推出的Quartus电路仿真环境中,结合使用AHDL语言和原理图仿真来完成VB解码器的FPGA实现。 2.1解码器的总体实现方案解码器的总体方案如图2所示。

来自发送方的数据在信道上传输,经过同步和信道估计后,根据CSI信息对维特比进行量化,并且对量化后的信息进行解交织并发送至维特比解码单元。从前端接收到代码字后,它必须首先在发送方的删除位置填写特定的错误代码元素。

该功能完成。

公司: 深圳市捷比信实业有限公司

电话: 0755-29796190

邮箱: momo@jepsun.com

产品经理: 聂经理

QQ: 2215069954

地址: 深圳市宝安区翻身路富源大厦1栋7楼

更多资讯

获取最新公司新闻和行业资料。

- double sum = 0.0; for(int i = 0; i < n; i++) { if(resistors[i] > 0) { sum += 1.0 / resistors[i]; 在C语言中计算并联电阻的总电阻是一个常见的应用问题,它涉及到基本的物理知识与编程技巧的结合。并联电路中的总电阻可以通过所有并联电阻倒数的和的倒数来计算。首先,我们需要定义一个函数来处理这一计算过程。例如...

- 五向开关DC12(V)0.05(A):应用与技术参数 五向开关DC12(V)0.05(A)是一种电子元件,它在电路设计和设备控制中发挥着重要作用。这种开关通常用于需要控制多个方向或功能的应用场景,例如遥控器、游戏控制器或是小型电子设备的导航按钮等。五向开关能够提供上、...

- ALPS编码器在工业自动化中的应用与PLC通信实现详解 ALPS编码器在工业自动化中的核心作用ALPS编码器作为高精度位置检测装置,广泛应用于数控机床、机器人、传送带系统等工业自动化设备中。其具备高分辨率、抗干扰能力强、响应速度快等特点,能够实时反馈机械部件的位置与运...

- AC-DC转换器中二次侧协定译码器的关键作用与实现机制 AC-DC转换器中二次侧协定译码器的核心功能解析在现代电源管理系统中,AC-DC转换器扮演着至关重要的角色,尤其在消费电子、工业控制和通信设备中广泛应用。其中,二次侧协定译码器(Secondary Side Protocol Decoder)作为实现高效、...

- 德国P+F接近开关:工业自动化中的关键组件 德国P+F接近开关是工业自动化领域中不可或缺的一部分,它们被广泛应用于各种机械设备和生产线上,以实现非接触式的物体检测。这种传感器通过电磁场或射频技术来识别目标物体,无需与物体直接接触即可检测其存在与否,...

- GB/T 1- 整流变压器与1.24V参考电压组件协同设计实践 GB/T 1- 整流变压器与1.24V参考电压组件的协同优化设计随着电力电子设备向智能化、高效化发展,整流变压器的设计不再局限于简单的变压功能,而是需要集成先进的控制策略。在此背景下,1.24V参考电压组件与国家标准 GB/T 1- 的...

- ALPS编码器与PLC通信技术详解:实现高精度位置控制的实践方案 ALPS编码器与PLC通信技术详解在现代自动化控制系统中,位置反馈是实现精准控制的关键环节。ALPS编码器作为高精度、高可靠性的旋转或线性位移传感器,广泛应用于工业机器人、数控机床、传送带等设备中。而可编程逻辑控制器...

- GB/T标准下讯号切换器与多任务器的技术规范与应用解析 引言在现代电子系统中,讯号切换器与多任务器作为关键的信号管理设备,广泛应用于工业自动化、通信系统、医疗设备及智能楼宇等领域。根据中国国家标准GB/T的相关规定,这些设备的设计、性能测试与安全要求均有明确的技...

- 现货SMC磁性开关D-90、D-A93 D-A73:高效可靠的自动化控制选择 现货供应的SMC磁性开关D-90、D-A93和D-A73型号是工业自动化领域中不可或缺的传感设备。这些开关主要用于检测气缸活塞的位置,通过内置的磁感应元件来实现非接触式的信号传输。它们在设计上具备小巧紧凑的特点,能够轻松安装...

- GB/T标准下讯号切换器的技术规范与应用解析 GB/T标准下讯号切换器的技术规范与应用解析随着信息化和智能化技术的快速发展,讯号切换器作为音视频系统中的核心组件,其性能与标准化程度直接影响系统的稳定性和兼容性。根据中国国家标准GB/T的相关规定,讯号切换器在...

- 整流变压器在电力系统中的作用及其GB/T标准符合性分析 引言整流变压器是电力电子系统中的核心组件之一,主要用于将交流电转换为直流电,广泛应用于轨道交通、电解工业、高压直流输电(HVDC)及新能源储能系统中。根据中国国家标准GB/T系列,整流变压器的设计、绝缘等级、温升...

- 爱普瑞BRT-205L-T:高效实用的智能设备 爱普瑞BRT-205L-T是一款高效实用的智能设备。该产品以其卓越的性能和便捷的操作体验,受到了广大用户的青睐。首先,在设计上,爱普瑞BRT-205L-T采用了先进的技术理念,确保了其在同类产品中的领先地位。无论是外观设计还是内...

- 德国福P+F接近开关:自动化控制领域的高效解决方案 德国福P+F公司是世界著名的传感器制造商之一,其生产的接近开关在自动化控制领域拥有极高的声誉。福P+F接近开关采用先进的传感技术,能够在无需物理接触的情况下检测到目标物体的存在,这不仅减少了机械磨损,还大大提...

- 如何选择符合GB/T标准的讯号切换器?关键参数全解析 如何选择符合GB/T标准的讯号切换器?关键参数全解析在企业、政府、学校等机构采购音视频设备时,选择一款符合国家推荐性标准GB/T的讯号切换器至关重要。这不仅关乎系统稳定性,也直接影响后期维护成本与合规性审查。1. 核...

- 德国P+F近接开关:高精度与可靠性的典范 德国P+F公司,即Pepperl+Fuchs,是全球领先的传感器技术和自动化领域的专家。其生产的近接开关(也称为接近传感器或接近开关)是工业自动化领域不可或缺的一部分。这些设备能够无接触地检测物体的存在,广泛应用于各种行业...

- ABB塑壳断路器(S系列.T系列): 高效可靠的配电解决方案 ABB塑壳断路器以其卓越的性能和可靠性在电气行业中享有盛誉。S系列和T系列作为ABB断路器中的佼佼者,分别针对不同的应用领域提供了高效且灵活的解决方案。S系列塑壳断路器设计紧凑、功能全面,适用于各种工业及商业环境...

- 符合GB/T标准的讯号切换器性能评估与选型指南 GB/T标准下讯号切换器的质量保障体系在中国,符合国家标准GB/T系列规范的讯号切换器需通过严格的电磁兼容性(EMC)、安全性、环境适应性等多项检测。这些标准不仅确保产品可靠性,也为企业采购提供明确的技术依据。1. 关键...

- 德国P+F电感式接近开关:工业自动化的关键组件 德国P+F(*福)是一家在传感器技术和自动化领域享有盛誉的公司。其电感式接近开关作为产品线中的重要一员,在工业自动化控制领域扮演着关键角色。这种类型的接近开关利用电磁感应原理来检测金属物体的存在与否,无需与目...

- 欧姆龙V/Z/D4MC等系列行程开关:性能与可靠性的典范 V/Z/D4MC等系列欧姆龙行程开关是工业自动化领域中不可或缺的组成部分。这些行程开关以其出色的性能和可靠性在各种应用中发挥着关键作用。例如,V系列行程开关具有紧凑的设计,适用于空间有限的应用环境;而Z系列则以其卓...

- 影像译码器与数码管间电阻选型的科学依据与实际应用解析 影像译码器与数码管间电阻的重要性概述在数字显示系统中,影像译码器(如74LS47、CD4511等)负责将二进制编码转换为七段码,驱动数码管显示数字。然而,直接连接译码器与数码管可能导致电流过大或电压不匹配,从而损坏器...